# ビデオカメラへのパノラマ映像生成機能の実装について

長瀬 幸規 † 川村 尚生 ‡ 菅原 一孔 ‡ † 鳥取大学 大学院 工学研究科 知能情報工学専攻 ‡ 鳥取大学 工学部 知能情報工学科

# 1. はじめに

1台のビデオカメラでテレビ会議場を撮影する場合,会議場全体を広範囲に渡って撮影すると話者の表情を読み取ることが難しい.また逆に,表情が分かるように撮影すると会議場の狭い範囲しか撮影できない.

そこで,会議場のパノラマ映像と話者映像を1つの映像に合成する機能をビデオカメラに組み込んだパノラマカメラを開発することでこの問題の解決を試みた.

# 2. パノラマカメラ

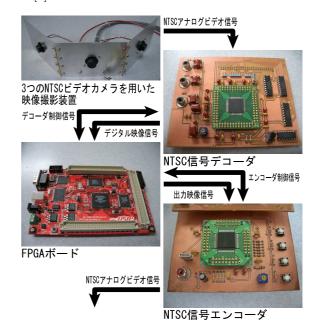

開発したパノラマカメラは,以下の各装置から成り立っている.図1に各装置と信号の流れを示す.

- 3 つの NTSC ビデオカメラを用いた映像撮影装置 3 つの超小型 NTSC ビデオカメラを用い,そのカメラ同士の角度が変更可能な装置である.この装置を用いることにより,容易にパノラマ映像中の 3 つの撮影映像の境界線の変更が可能になる.

- NTSC 信号デコーダ

3 チャンネルの NTSC アナログビデオ信号入力を持ち、そのチャンネルを切り替えることにより、3 つの入力信号をそれぞれ個別の RGB 各 8[bit] のデジタル映像信号に変換する.NTSC 信号デコード LSI としては、沖電気工業株式会社の「MSM7664B」 [1] を使用した.

# ● FPGA ボード

パノラマカメラの主な機能は FPGA の内部回路 やメモリなどで構成される.この FPGA ボードに は20万ゲート相当の FPGA(Field Programmable Gate Array) と呼ばれる書き換え可能な大規模集 積回路と,それに独立のバスで接続された2つの 36[bit] 幅で容量 18[Mbit] の SSRAM(Synchronous SRAM) が搭載されている.

NTSC 信号エンコーダ

RGB 各 8[bit] のデジタル映像信号を NTSC アナロ グビデオ信号に変換する.NTSC 信号エンコード LSI としては,沖電気工業株式会社の「MSM7654」 [2] を使用した.

図 1: 各装置と信号の流れ

次に,パノラマカメラで行われている各処理の流れ を示す.

- 1. 3 つの NTSC ビデオカメラで撮影された映像は,個別の NTSC アナログビデオ信号として出力される.

- 2. カメラから出力された各信号は,NTSC信号デコー ダによって RGB デジタル映像信号に変換される.

- 3. デジタル化された3つの映像信号は,FPGAボード上の撮影映像用メモリに独立して書き込まれる.

- 4. メモリに書き込まれた 3 つの撮影映像を基に, FPGA の内部回路を用いて映像サイズの縮小および出力映像の合成が行われ,その映像は出力映像用メモリに書き込まれる.

- 5. 出力映像用メモリに書き込まれた出力映像は, NTSC 信号エンコーダによって再び NTSC アナログビデオ信号に変換され,出力される.

## 3. FPGA での処理

VHDL(Very high speed integrated circuit Hardware Description Language) [3] [4] を用いて以下の処理をFPGAに実装した.

#### 3.1 映像サイズの縮小

パノラマ映像を生成する際,メモリに保存したままの撮影映像サイズ  $(320\times240 [\mathrm{pixel}])$  でパノラマ化すると,パノラマ映像の映像サイズが想定している出力映像の映像サイズ  $(640\times480 [\mathrm{pixel}])$  よりも大きくなる.そこで,映像サイズを  $3/4(240\times180 [\mathrm{pixel}])$  に縮小する.

#### 3.2 出力映像の合成

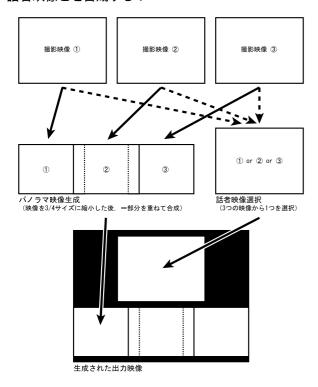

図 2 に示すように,ある決められた距離と角度で配置された3 つの超小型ビデオカメラで撮影した映像を,3/4 サイズに縮小しパノラマ状につなぎ合わせたパノラマ映像と,それらの映像の中から選択された1 つの話者映像とを合成する.

図 2: 出力映像合成の様子

# 3.3 NTSC 信号デコーダ, エンコーダの制御

NTSC 信号デコーダ, エンコーダの出力するタイミング信号に合わせて, デジタル映像信号の取り込みまたは出力を行う.

## 4. 動作実験

動作実験は,装置から出力された NTSC アナログビデオ信号をテレビモニタに入力することで行った.

実際に動作実験中の画面の様子を図3に示す.画面 下部の映像は3つの撮影映像を縮小し生成されたパノ ラマ映像である.また,画面上部の映像は3つの撮影映像の中から FPGAボード上のプッシュスイッチによって1つ選択された話者映像である.

映像表示速度の測定を行ったところ,現在は5[フレーム/秒] 程度であり,実際に人物が動いてから画面に反映されるまでに若干の遅延があった.

図 3: 動作実験中の画面

# 5. おわりに

3 つの NTSC ビデオカメラを用いた映像撮影装置, NTSC 信号デコーダ, NTSC 信号エンコーダ, FPGA の内部回路を開発しパノラマカメラの基本的な機能を実現したが, 現在のところ話者映像の選択はプッシュスイッチによる手動操作のため, 実用段階にはまだ至っていない.

そのため今後は話者映像の選択を,現在の手動操作ではなく自動化することを目指す.その具体的な方法としては,複数のマイクロフォンを設置し取得した音声を  $\mathrm{FPGA}$  の内部で処理することで,話者の方向を推定することを考えている.また,パノラマ映像を生成する際,3 つの  $\mathrm{NTSC}$  ビデオカメラ映像の境界線を自動的に検出する内部回路を  $\mathrm{FPGA}$  上に構築することを考えている.

### 参考文献

- [1] 沖電気工業株式会社: MSM7664B データシート, 沖電気工業株式会社 (2001)

- [2] 沖電気工業株式会社: MSM7654 データシート, 沖電気工業株式会社 (2003)

- [3] 長谷川 裕恭: VHDL によるハードウェア設計入門, CQ 出版社 (2002)

- [4] 森岡 澄夫: HDL による高性能ディジタル回路設計, CQ 出版社 (2002)